# **CHIMERA**

## RELEASE 1

## 5-speed 2-port network impairment emulator

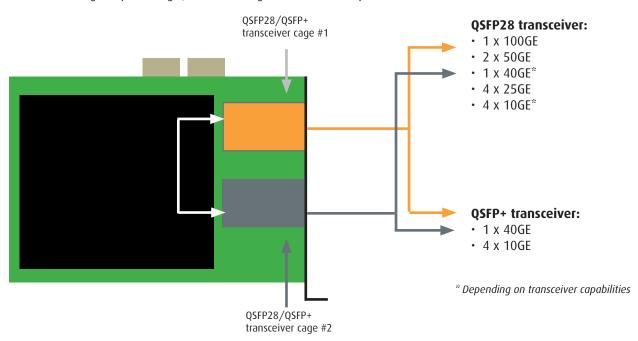

Chimera can emulate network impairments at five Ethernet network speeds: 100GE, 50GE, 40GE, 25GE and 10GE. This unique flexibility is provided via two physical transceiver cages, both supporting QSFP28 and QSFP+ transceivers.

The result is a versatile solution that provides consistent, accurate, well-defined and repeatable impairments to the traffic between DUTs – in the lab. This is ideal for benchmarking, stress/negative, "what-if" and regression testing of network infrastructure and Ethernet equipment capable of supporting 100GE such as switches, routers, NICs and fronthaul/ backhaul platforms.

#### **TOP FEATURES**

- 5-speed flexibility: 100GE, 50GE, 40GE, 25GE and 10GE

- 2-port capacity

- · Integration with Valkyrie traffic generator

- Price/performance

- · Ease of use

- Free software (incl. ValkyrieManager and XenaScripting)

- · Free tech support product lifetime

| PORT LEVEL FEATURES                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Interface category                                 | QSFP28 • 100G, 50G, 40G*, 25GE and 10G* Ethernet  QSFP+ • 40G, 10G Ethernet  * Depending on transceiver capabilities                                                                                                                                                                                                                                                                                                                           |  |

| Total number of test ports (software configurable) | 2x100G, 2x50G, 2x40G, 2x25G, and 2x10G Ethernet (planned 2x100G, 4x50G, 2x40G, 4x25G, and 4x10G Ethernet)                                                                                                                                                                                                                                                                                                                                      |  |

| Interface options                                  | Each cage  • 1 x 100GBASE-SR4/LR4/CR4, or 802.3bj standard • 2 x 50GBASE-SR2/LR2/CR2, or Consortium** • 1 x 40GBASE-SR4/LR4/CR4, or 802.3ba • 4 x 25GBASE-SR/LR/CR, or 802.3by/Consortium** • 4 x 10GBASE-SR/LR/CR 802.3ae  Actual interface options depend on the capabilities of the inserted transceiver. Both cages must run with the same base interface configuration (e.g. 2 x 50G).  ** As defined by 25/50 GigabitEthernet Consortium |  |

| Auto Negotiation and Link Training                 | IEEE 802.3 Clause 73, Auto-negotiation IEEE 802.3 Clause 72, Link training                                                                                                                                                                                                                                                                                                                                                                     |  |

| Forward Error Correction (FEC)                     | RS-FEC (Reed Solomon) FEC, IEEE 802.3 Clause 91 (100GE)<br>RS-FEC (Reed Solomon) FEC, IEEE 802.3 Clause 108 (25GE)<br>RS-FEC (Reed Solomon) FEC, 25/50G Ethernet Consortium (25/50GE)                                                                                                                                                                                                                                                          |  |

| Number of transceiver module cages                 | 2 x QSFP28/QSFP+                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Port statistics                                    | Link state, FCS errors, pause frames, ARP/PING, error injections, training packet                                                                                                                                                                                                                                                                                                                                                              |  |

| Adjustable Inter Frame Gap (IFG)                   | Configurable from 16 to 56 bytes, default is 20B (12B IFG + 8B preamble)                                                                                                                                                                                                                                                                                                                                                                       |  |

| Transmit line rate adjustment                      | From -400 to 400 ppm in steps of 0.001 ppm (shared across all ports)                                                                                                                                                                                                                                                                                                                                                                           |  |

| Field upgradeable                                  | System is fully field upgradeable to product releases (FPGA images and software)                                                                                                                                                                                                                                                                                                                                                               |  |

| Tx disable                                         | Enable/disable of optical laser or copper link                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Oscillator characteristics                         | <ul> <li>Initial Accuracy is 3 ppm</li> <li>Frequency drift over 1st year: +/- 3 ppm (over 15 years: +/- 15 ppm)</li> <li>Temperature Stability: +/- 20 ppm (Total Stability is +/- 35 ppm)</li> </ul>                                                                                                                                                                                                                                         |  |

## RELEASE 1

| 100/50/40/25GE FRAMED PRBS AND PCS LAYERS |                                                                                                                                                                           |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Payload Test pattern                      | PRBS 2^31                                                                                                                                                                 |  |

| Error Injection                           | Manual single shot bit-errors or bursts, automatic continuous error injection                                                                                             |  |

| Frame size and header                     | Fixed size from 56 to 9200 bytes, any layer 2/3/4 frame header                                                                                                            |  |

| Alarms                                    | Pattern loss, bit-error rate threshold                                                                                                                                    |  |

| Error analysis                            | bit-errors: seconds, count, rate per physical lane                                                                                                                        |  |

| PCS virtual lane configuration            | User-defined skew insertion per Tx virtual lane, and user defined virtual lane to SerDes mapping for testing of the Rx PCS virtual lane re-order function.                |  |

| PCS virtual lane statistics               | Relative virtual lane skew measurement (up to 2048 bits), sync header and PCS lane marker error counters, indicators for loss of sync header and lane marker, BIP8 errors |  |

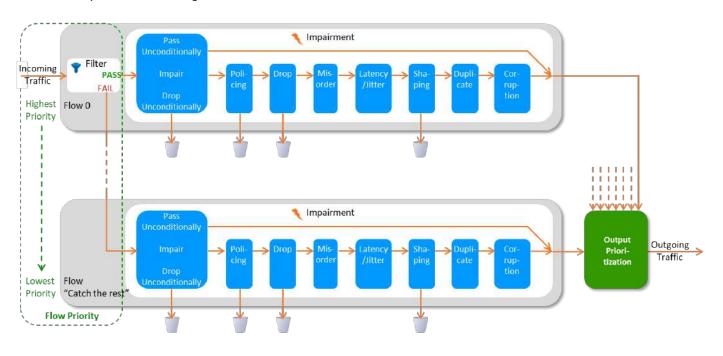

| FLOWS                    |                                                                                                                                                                                                                                                        |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of flows per port | Up to 8 including default flow                                                                                                                                                                                                                         |

| Flow filter definition   | MAC Source and Destination Address VLAN Tag (C-Tag and S-Tag) MPLS Label IPv4 Source and Destination Address IPv4 DSCP/TOS IPv6 Source and Destination Address UDP/TCP port numbers Up to 6 consecutive bytes in the packet Xena Test Payload ID (TID) |

| Multiflow output control | FIFO Round Robin Flow Priority Strict Priority (VLAN priority, MPLS priority, IP (DSCP/TOS (IPv4) or Traffic Class (IPv6))                                                                                                                             |

| Libraries                | Libraries of own impairments MEF-18 ITU-T G.8261 G.1050/TIA-921                                                                                                                                                                                        |

| IMPAIRMENT PER FLOW |                                                                                                                                                                                                                                        |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| General             | Impairments can be changed dynamically                                                                                                                                                                                                 |  |

| Packet Manipulation | Packet drop (Random, Burst, Periodic, BER, Gilbert-Elliott) Packet drop up to 100%. Step size: 0.0001%.  Duplication Mis-ordering Corruption (Ethernet Frame FCS, IP header Check Sum error, UDP Check Sum error, TCP Check Sum error) |  |

| Latency / jitter    | Constant Uniform Exponential Accumulate & Burst Jitter (Gaussian) Max latency 160000 µsec (100GE wire-speed) Step size 1 ns, accuracy: +/- 150 ns                                                                                      |  |

| Bandwidth Control   | Policing Shaping                                                                                                                                                                                                                       |  |

| CAPTURE & FLOW DISCOVERY           |                                               |

|------------------------------------|-----------------------------------------------|

| Capture criteria                   | TBD                                           |

| Capture start/stop triggers        | TBD                                           |

| Capture limit per packet           | TBD                                           |

| Wire-speed capture buffer per port | TBD                                           |

| Flow discovery                     | Define flow filters based on captured traffic |

| ADVANCED PHY FEATURES          |                                                                                                                                                                                                                |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit Equalization Controls | <ul> <li>Tx Transmit Equalization Controls Pre-emphasis</li> <li>Tx Attenuation</li> <li>Tx Post-emphasis Signal Integrity Analysis</li> <li>Rx Optional Auto-Tune of PHY 50 &amp; 25Gbps Rx SerDes</li> </ul> |

## How Chimera processes incoming traffic:

## RELEASE 1

## One module - multiple options

Chimera has 2 transceiver cages. The type of transceiver used determines the speeds and number of ports available. The port number / speed configuration must be the same for both cages and this is defined using ValkyrieManager, Xena's traffic generation and analysis software.

## **SPECIFICATIONS**

## **Dimensions**

## 1U ChimeraCompact

- W: 19" (48.26 cm) 1.75" (4.45 cm) 9.8" (25 cm) • H:

- Weight: 10 lbs (4.5 kg)

#### Max. Noise

- ValkyrieCompact: 49 dBa

- · ValkyrieBay: 58.5 dBa

### Environmental

- · Operating Temperature: 10 to 35° C

- Storage Temperature: -40 to 70° C

- · Humidity: 8% to 90% noncondensing

#### Regulatory

FCC (US), CE (Europe)

### Power

- AC Voltage: 100-240V

- Frequency: 50-60Hz

- · Max. Power: 90W (ValkyrieCompact) / 120W (ValkyrieBay)

- · Max. Current: 0.8A with 120V supply, and 0.4A with 240V supply